Speichererweiterung für Aufzeichnung (A/D-Wandler)

Da der P89LPC932/935 nur über einen 512-Byte großen XRAM-Bereich verfügt, können größere Datenmengen, die z. B. bei einer kontinuierlichen A/D-Wandlung über einen gewissen Zeitraum entstehen, nicht zwischengespeichert werden. Um den RAM-Speicher zu vergrößern, sind folgende Möglichkeiten denkbar:

· Verwendung eines zusätzlichen FIFOs

Es werden handelsübliche FIFOs verwendet.

Vorteile:

Einfache Ansteuerung des µControllers

Nachteile:

Hoher Preis

Geringe Speichertiefe

Es kann nicht auf eine beliebige Speicheradresse zugegriffen werden.

· Verwendung von SPI/I²C-RAM-Speicher(n)

Es werden handelsübliche RAM-Speicher verwendet, die via SPI- bzw. mit dem I²C-Bus angesteuert werden.

Vorteile:

Sehr einfache Ansteuerung (es werden nur zwei bis drei zusätzliche Portpins belegt).

Nachteile:

Es gibt nur kleine RAM-Speicher.

Langsame Übertragungsgeschwindigkeit (I²C-Bus)

· Aufbau eines eigenen Adress-/Datenbusses mit externem RAM

Es wird der komplette Adress-/Datenbus mit Adress-Latch nachgebildet. Die Schreib-/Lesesignale werden mit zusätzlichen Portpins realisiert.

Vorteile:

Beliebige Speichergröße möglich

Nachteile:

Es werden sehr viele zusätzliche Portpins für die Nachbildung des Adress-/Datenbusses und der Steuersignale benötigt.

· Vereinfachter Aufbau eines eigenen Adress-/Datenbusses mit externem RAM

Für den Adressbus wird ein 12-bit Counter eingesetzt. Dieser kann mit Hilfe von Portpins zurückgesetzt, bzw. getaktet werden. Die Steuersignale für den Schreib-/Leseimpuls werden mit zwei zusätzlichen Portpins realisiert.

Vorteile:

Beliebige Speichergröße möglich. Nur wenige zusätzliche Steuerleitungen werden benötigt.

Nachteile:

Keine direkte Adressierung einer bestimmten RAM-Adresse möglich.

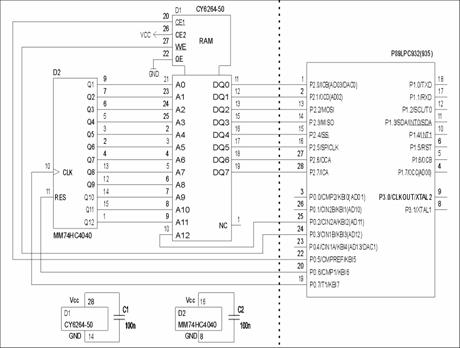

Für die Speichererweiterung wurde der vereinfachte Aufbau verwendet, da die A/D-Daten nur in zeitlicher Reihenfolge in aufeinander folgenden Adressen zwischengespeichert werden müssen. Den Schaltungsaufbau können sie der Abbildung 54 entnehmen. Port 2 wird nur während dem Schreib-/Lesevorgang der Daten benötigt. Ansonsten ist er frei verfügbar. Die Ansteuerung von A12 kann auch über einen kaskadierten 74HC4040 erfolgen. Dies hätte auch noch den Vorteil, dass größere SRAM-Bausteine eingesetzt werden können.

|

|

Abbildung 54 Aufbau einer externen Speichererweiterung 8k (getaktete Adressierung)

Erstellen sie das folgende Projekt, um die Ansteuerung und das SRAM testen zu können. Für das Schreiben bzw. Auslesen des SRAMs werden zwei eigenständige Funktionen (siehe Listing 56, und ) erstellt. In main() wird das SRAM mit Hilfe einer Schleife zuerst beschrieben (siehe ) und danach ausgelesen (siehe ). Entspricht der ausgelesene Wert nicht dem erwarteten, wird das Programm bei der while(1) Bedingung gestoppt. An diese Stelle kann jetzt eine Fehlerausgabe, z. B. über die serielle Schnittstelle oder eine Ausgabe auf dem LCD, erfolgen.

|

Projektname |

Verzeichnis |

Verwendete Sourcemodule |

|

TestExtRAM |

Test_ExtRAM |

TestExtRAM.c |

Tabelle 60 TestExtRAM

|

|

#include <REG932.H> // Definition der SRAM-Groesse #define SRAMSIZE 8192

// Definition der Steuerleitungen (SRAM) sbit A12 = P0^2; sbit _WE = P0^3; sbit _CS1= P0^5; // Definition der Steuerleitungen (74HC4040) sbit CLR = P0^6; sbit CLK = P0^7;

v_ClearCnt(void) { CLR = 1; // Counter loeschen CLR = 0; A12 = 0; // A12 zuruecksetzen }

void v_WriteVal(unsigned char ucVal) { P2M1 = 0x00; // Port 2 in Push-Pull P2M2 = 0xFF; P2 = ucVal; // Wert einschreiben // Schreibimpuls erzeugen (Inhalt von P2 wird eingeschrieben) _CS1 = 0; _WE = 0; _WE = 1; _CS1 = 1; CLK = 0; CLK = 1; // auf naechste Adresse setzen }

unsigned char uc_ReadVal(void) { unsigned char ucResult; P2M2 = 0x00; // Quasi-Bidir. P2M1 = 0x00; P2 = 0xFF; // Port freigeben _WE = 1; _CS1 = 0; ucResult = P2; // Wert einlesen _CS1 = 1; CLK = 0; CLK = 1; // auf naechste Adresse setzen return (ucResult); }

void main(void) { unsigned int uiLoop;

P0M1 = P0M1 & 0x13; // Port 0 in Push-Pull P0M2 = P0M2 | 0xEC; P0 = P0 | 0xEC; // Portpins auf 1 setzen

v_ClearCnt(); // Speicher mit Werten beschreiben for (uiLoop = 0; uiLoop < SRAMSIZE; uiLoop++) { v_WriteVal((unsigned char)uiLoop); if (uiLoop == 4096) A12 = 1; } v_ClearCnt(); // Speicher auslesen und Werte ueberpruefen for (uiLoop = 0; uiLoop < SRAMSIZE; uiLoop++) { if (uc_ReadVal() != (unsigned char) uiLoop) { // Haelt im Fehlerfall an, wenn ein RAM-Inhalt while(1); // nicht dem erwarteten Wert entspricht. } if (uiLoop == 4096) A12 = 1; } while(1); } |

Listing 56 Inhalt von TestExtRAM.c

Das Schreiben und Lesen kann noch optimiert werden, wenn der Port P2 nicht anderweitig benutzt wird. In diesem Fall kann die Umschaltung des Ports zwischen Quasi-Bidirektional und Push-Pull (siehe und ) vor dem Schleifendurchlauf (siehe und ) erfolgen.